# ISSN:2229-6107

E-mail : editor.ijpast@gmail.com editor.ijpast@.in

Vol 9, Issuse 2. JUNE 2019

## A General Cost-effective Design Structure for Probabilistic-Based Noise-Tolerant Logic Functionsin Nanometer CMOS Technology

Mr.JADA LINGAIAH, Mr.JEEDIMADLA VENKATESHAM, Miss K.SWATHI, K MANISHA

*Abstract*—Noise-immunity of a logic gate or a circuit is now an important design criterion with dimension scaling to nanometers. Two noise-immune design structures based on *Markov random field* (MRF) have been proposed in [1], [2] and [3]. These design structures can achieve an excellent noise-immunity but with a large number of redundant transistors. In this paper, a general noise-immune design structure easy to implement has been proposed. It can achieve nearly the same noise-immunity as *Master-and-Slave* MRF (MAS MRF) [3] but with a significantly less area penalty. Basic logic gates are simulated and comparison of different circuits based on different design structures is presented. These simulations are based on the *Berkeley Predictive Technology Model* (BPTM) 65nm CMOS Technology [4] and ST 65nm CMOS models.

Index Terms-Markov random field (MRF), noise-immunity, general cost-effective structure, CMOS

#### INTRODUCTION

The CMOS dimension scaling technology has dramatically improved the performances of transistors and devices in the past decades. In order to keep the power dissipation constant or at a low degree, the supply voltage should scale linearly with the size [5]. In this situation, the reduction of noise margin makes the transistors and devices working in a noisy signal environment. As a result, the transistors in nanometers are much more prone to soft errors, and thus the noise-immune ability of a logic gate or a circuit becomes an important designcriterion [6].

For the intrinsic random nature of noise, traditional fault- tolerant design methodologies based on hardware redundancy,

e.g. Triple-Modular-Redundancy (TMR) [7], Cascade TMR (CTMR) [8], are not capable to obtain noiseimmunity. The noise interferes the input signal of each module and de- grades the right judgment of the majority voter. The NAND- multiplexing methodology proposed by Von Neumann [9] can produce the reliable result using unreliable components. However, it needs an extremely high degree of redundancy [10]. The reconfiguration technology is more effective to deal with manufacturing defects or permanent faults and requires enormous amounts of redundancy [11]. Therefore, the traditional approaches are not effective to attain noise-immunity for the random and dynamic nature of noise. Probabilistic-based technologies are more suitable to

deal with this problem [12], [13], [14]. One of the promising noise-tolerant probabilistic-based designs is proposed in [1], which is based on Markov random field (MRF) [15]. Accord- ing to Nepal et al. [1], the reliability or the noise-immunity of a circuit can be improved by maximizing the joint probability of valid input-output pairs with a cost of hardware redundancy. Furthermore, it was optimized in [2] in order to reduce its areapenalty. In [3], a Master-and-Slave MRF (MAS MRF) design structure was proposed by Wey et al., which can obtain nearly the same noise-immune ability as structures in [1], [2] but with fewer transistors. In addition to the area overcost, another disadvantage of approaches proposed in [1], [2], [3] is that they did not propose a general design structure applicable to all the basic logic gates. In other words, we should design every single logic gate specially. Also another approach based on MRF was proposed in [16], which is based on Differential Cascode Voltage Switch (DCVS). However, this methodology is just desirable for an inverter.

ASSISTANT PROFESSOR<sup>1,2,3</sup>, STUDENT<sup>4</sup> Department of ECE Arjun College Of Technology & Sciences Approved by AICTE& Affiliated to JNTUH SPONSORED BY BRILLIANT BELLS EDUCATIONAL SCOITEY In this work, we propose a general cost-effective noiseimmune design structure of logic functions. Compared with MAS MRF structure, our proposed structure can be imple- mented to all the basic logic gates with nearly the same noise- immune ability and a much less area cost. Furthermore, this generality means that the proposed structure applies also for functions involving several logic gates and is therefor much more cost effective than the solutions mentioned before.

This paper is organized as follows. Section II reviews the preliminaries on MRF theory and the previous noiseimmune circuit design structures. The proposed design structure is described in Section III. Section IV shows the simulation results and comparisons of different design structures. Simula-tions have been done in SPICE using the *Berkeley Predictive Technology Model* (BPTM) 65nm CMOS Technology [4] and in Spectre based on ST 65nm CMOS models. Finally, discussions and conclusions are given in Section V.

which can be defined either continuous or discrete according to

For example, for a MAS MRF NAND logic gate, the minterms with  $\frac{1}{2}$  belong to group "1" and the minterms with

$\square_2$  belong to group "0". It reduces the valid states generator

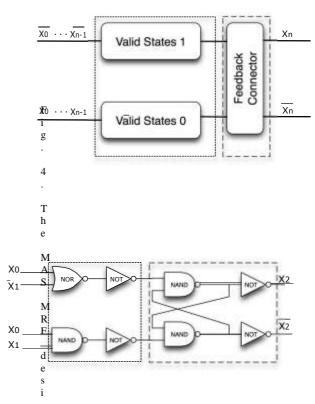

from four NAND gates in Fig. 3 to one NAND gate, one NOR gate plus two inverters. As for the feedback loop, it contains only two NAND gates and two inverters while in Fig. 3, five NAND gates and seven inverters are required. The MAS MRFNAND gate is presented in Fig. 5.

Master Slave

minterms reduction, an optimized expression of equation (6) is given as:

Fig. 5. The two-input MAS MRF MAND gate implementation.

I. PROPOSED GENERAL LOGIC GATES DESIGN

We propose a general Cost-Effective Noise-Tolerant circuit

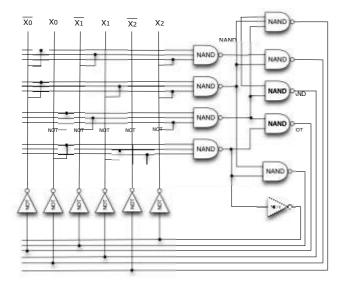

Fig. 3. The two-input MRF NAND gate implementation. The two inputs are  $\Box_0$  and  $\Box_1$ , the output is  $\Box_2$ .

According to the Boolean simplification and valid

$$\Box (\Box_{0'} \Box_{1'} \Box_{2}) = - \sum_{\Box_{\Box}} \Box_{\Box} (\Box_{0'} \Box_{1'} \Box_{2})$$

$$= -(\Box_{\underline{\Box}}^{-} \Box_{1} \overline{\Box}_{2} + \Box_{0} \overline{\Box}_{1} \Box_{2} + \Box_{0} \Box_{1} \overline{\Box}_{2} + \Box_{0} \Box_{1} \Box_{2})^{-}$$

$$= - ((\Box_{0} + \overline{\Box}_{1}) \Box_{2} + (\Box_{0} \Box_{1}) \overline{\Box}_{2})$$

(7)

According to equation (7), Nepal *et al.* optimized the generation of the valid states and thus reduced the transistor numbers, as proposed in [2].

Another design structure is MAS MRF [3]. Its structure is shown in Fig. 4. The *Master* subset generates the valid states and the *Slave* subset is the feedback loop. The *Master* subset divides the valid states into the valid groups "0" and "1". All the valid states with the output value 1 compose the "1" group and those with output value 0 compose "0" group. Compared with [1], another advantage of MAS MRF is the redesign of the feedback loop, which reduces the transistor number and the hardware complexity.

design structure based on Markov Random Field, named CENT MRF. In order to illustrate the proposed approach, take account of the NAND gate. Its corresponding energy function is given in equation (7). We know that

where  $\Box_{\Box\Box\Box}(\Box_0, \Box_1)$  is the logic function of a NAND gate. Its input signals are  $\Box_0$ ,  $\Box_1$  and its output signal is  $\Box_2$ .

We propose to proceed in the same way to obtain the energyfunction of any logic gate. Especially, this produces the energy function for the basic logic gates as shown bellow.

#### A. Simulation results (SPECTRE)

Spectre simulator has been used for simulations of basic logic gates as well as more complex logic combinational func- tions such as a one-bit full-adder (FA), a four-bit Ripple CarryAdder (RCA) and a (8, 4) Hamming Decoder to compare the noise-immunity of different design structures. We used the low threshold voltage and low power PMOS (plvtlp) and NMOS (nlvtlp) transistors of ST 65nm library. The supply voltage of the gates is  $1.2\Box$  and the temperature is  $25^{\circ}\Box$ . Different input signals with different *signal-noise-ratio* (SNR) were simulated and KLDs of output signal were quantified. If there were more than one output in the circuit, the output signal of *deepest-path*was treated as the representation.

The simulation results are shown in Fig. 10 to Fig. 14. TableII shows the comparison of the transistor number for different bench circuits.

#### II. DISCUSSIONS AND CONCLUSIONS

This paper proposed a general cost-effective noisetolerant circuit structure based on Markov Random Field. It is a general design approach easy to implement for all logic combinational

### REFERENCES

K. Nepal, R. Bahar, J. Mundy, W. Patterson, and A. Zaslavsky, "Designing nanoscale logic circuits based on markov random fields," *Journal of Electronic Testing*,

vol. 23, pp. 255–266, 2007, 10.1007/s10836-006-0553-9. [Online]. Available: http://dx.doi.org/10.1007/s10836-006-0553-9

K. Nepal, R. I. Bahar, J. Mundy, W. R. Patterson, and

Zaslavsky, "Optimizing noise-immune nanoscale circuits using principles of markov random fields," in *Proceedings* of the 16th ACM Great Lakes symposium on VLSI, ser. GLSVLSI '06. New York, NY, USA: ACM, 2006, pp. 149–152. [Online]. Available: http://doi.acm.org/10.1145/1127908.1127945

I.-C. Wey, Y.-G. Chen, C.-H. Yu, A.-Y. Wu, and J. Chen, "Design and implementation of cost-effective probabilisticbased noise-tolerant vlsi circuits," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol. 56, no. 11, pp. 2411–2424, nov. 2009.

http://ptm.asu.edu/.

L. B. Kish, "End of moore's law: Thermal (noise) death of integration in micro and nano electronics," *Physics Letters A*, vol. 305, pp. 144–149, Dec. 2002.

M. Haselman and S. Hauck, "The future of integrated circuits: A survey of nanoelectronics," *Proceedings of the IEEE*, vol. 98, no. 1, pp. 11–38, jan. 2010.

J. Han, J. Gao, P. Jonker, Y. Qi, and J. Fortes, "Toward hardware-redundant, fault-tolerant logic for nanoelectronics," *Design Test of Computers, IEEE*, vol. 22, no. 4, pp. 328 – 339, july-aug. 2005.

M. Hamamatsu, T. Tsuchiya, and T. Kikuno, "On the reliability of cascaded tmr systems," in *Dependable Computing (PRDC), 2010 IEEE 16th Pacific Rim International Symposium on*, dec. 2010, pp. 184–190.

J. V. neumann, *Probability Logic and the Synthesis of Reliable Organ- isms from Unreliable Components.* Princeton University Press, 1956.

J. Han and P. Jonker, "A system architecture solution for unreliable nanoelectronic devices," *Nanotechnology, IEEE Transactions on*, vol. 1, no. 4, pp. 201 – 208, dec 2002.

K. Nikolic, A. Sadek, and M. Forshaw, "Fault-tolerant techniques for nanocomputers," *Nanotechnology, Institute of physics publishing*, vol. 13, pp. 357 – 362, may 2002.

R. I. Bahar, J. Mundy, and J. Chen, "A probabilistic-based design methodology for nanoscale computation," in *Proceedings of the 2003 IEEE/ACM international conference on Computer-aided design*, ser. ICCAD '03. Washington, DC, USA: IEEE Computer Society, 2003, pp. 480–. [Online]. Available: http://dx.doi.org/10.1109/ICCAD.2003.17

X. Lu and X. Song, "A probabilistic logic for nanoscale devices," in *Integrated Circuit Design and Technology*, 2007. *ICICDT '07. IEEE International Conference on*, 30 2007-june 1 2007, pp. 1–4.

X. Lu, J. Li, and W. Zhang, "On the probabilistic characterization of nano-based circuits," *Nanotechnology, IEEE Transactions on*, vol. 8, no. 2, pp. 258–259, march 2009.

S. Z. Li, Markov Random Field Modeling in Computer Vision. Secau- cus, NJ, USA: Springer-Verlag New York, Inc., 1995.

Z. H. Lu, X. P. Yu, Y. Liu, J. N. Su, and C. H. Hu, "Design of nano-scale noise tolerant cmos logic circuits based on probabilistic markov random field approach," *Nanoscience and Nanotechnology Letters*, vol. 4, no. 9, pp. 914–918, sep 2012.

J. Besag, "spatial interaction and the statistical analysis of lattice systems," *Journal of the Royal Statistical Society, Series B (Method- ological)*, vol. 36, no. 2, pp. 192–236, 1974.

S. Kullback, *Information Theory and Statistics*. New York: Dover, 1969.

C. Shannon, "Communication in the presence of noise," *Proceedings of the IEEE*, vol. 86, no. 2, pp. 447 –457, feb. 1998.

View publication stats

H. Nyquist, "Certain topics in telegraph transmission theory," *Proceed- ings of the IEEE*, vol. 90, no. 2, feb. 2002.